Downsample a Signal

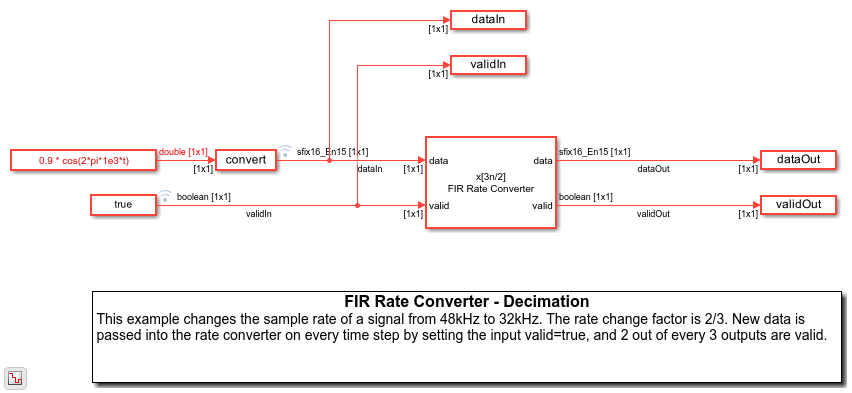

Convert a signal from 48 kHz to 32 kHz using the FIR Rate Converter block.

The source is a cosine input signal, sampled at 48kHz. The model passes a new data sample into the block on every time step by holding the input valid port true. After resampling, the output valid signal is true on only 2/3 of the time steps.

Open the Model

Configure the Model

Define the data rate parameters in the InitFcn callback.

Configure the FIR Rate Converter block. Use the default interpolation factor of 2 and decimation factor of 3. Use the firmpm function to design an equiripple FIR filter. In the Data Types group, set the Coefficients data type to fixdt(1,16,15) to accommodate the filter you designed.

Run the Model and Display Results

Run the model. Use the Logic Analyzer to view the input and output signals of the block. The blue icon in the model indicates streamed signals. Launch the Logic Analyzer from the model's toolstrip.

In the Logic Analyzer, note the pattern of validIn and the resulting validOut signal.

Generate HDL Code

To generate HDL code from the FIR Rate Converter block, right-click the block and select Create Subsystem from Selection. Then right-click the subsystem and in the HDL Coder app section click Generate HDL Code for a Subsystem.