Simscape Hardware-in-the-Loop Workflow

Simscape™ Hardware-in-the-Loop (HIL) workflow enables you to generate HDL code for your Simscape plant models and deploy the generated code onto generic field-programmable gate array (FPGAs), system on a chip (SoCs), or Speedgoat® FPGA I/O modules. By deploying the plant model to an FPGA board, you can accelerate the simulation of your model and simulate the model in real-time by using HIL simulations.

The Simscape HDL Workflow Advisor converts the Simscape plant model to an HDL-compatible implementation model from which you generate

HDL code. You can use the sschdladvisor function to open the Advisor and

run the tasks in it to generate an HDL implementation model. When you generate the HDL

implementation model, you can specify the data type precision (floating-point, such as

single or double, or fixed-point) for it. You can also

specify the insertion of validation logic in the implementation model and verify whether the

HDL implementation numerically matches the original Simscape algorithm.

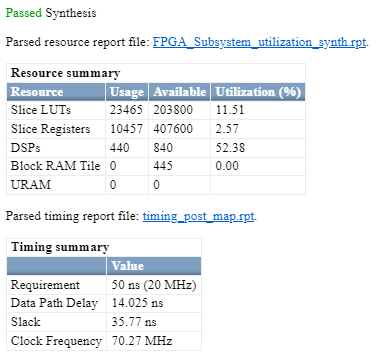

After you generate the HDL implementation model, you can use HDL Coder™ to generate code for this model and deploy the generated code onto target platforms by using the HDL Workflow Advisor.

Simscape Hardware-in-the-Loop Workflow Fundamentals

Categories

- Model Preparation

Prepare and configure your plant model

- HDL Code Generation

Generate HDL-compatible Simulink model for your plant model and generate HDL code

- Deployment

Deploy the generated HDL code onto target hardware

- Troubleshooting

Troubleshooting suggestions and solutions to address workflow issues

- Applications

Explore real-time application examples