Parallel Processing Unit

The parallel processing unit (PPU) is a specialized processing unit designed to speed up complex computations in an application model. Use PPU core to implement models with large data processing requirements or fast execution time requirements. This core is based on single instruction, multiple data (SIMD) vector DSP architecture and uses a specialized memory called vector closely coupled memory (VCCM) to speed up computations. Application models using the PPU core of Infineon® AURIX™ microcontrollers store the participating data in VCCM.

You can use Digital Port Read, Digital Port Write, PWM, TMADC, DSADC, Encoder, Interprocess Data Read, Interprocess Data Write, and Interprocess Data Channel blocks from SoC Blockset™ Support Package for Infineon AURIX Microcontrollers and SoC Blockset to design multicore models using the PPU core of AURIX TC4x microcontrollers.

The PPU core speeds up the computations by running the optimized functions generated using the code replacements technique. For more information on the technique, see What Is Code Replacement? (Embedded Coder). The PPU referenced model uses a function-call subsystem that uses CRL functionality to replace parts of generated code with hardware-specific code.

Code Replacement Library for PPU

The CRL technique optimizes the PPU run time. By default, the code generation does not contain the CRL functionality. Explore the available libraries to identify those that best meet the needs of your application.

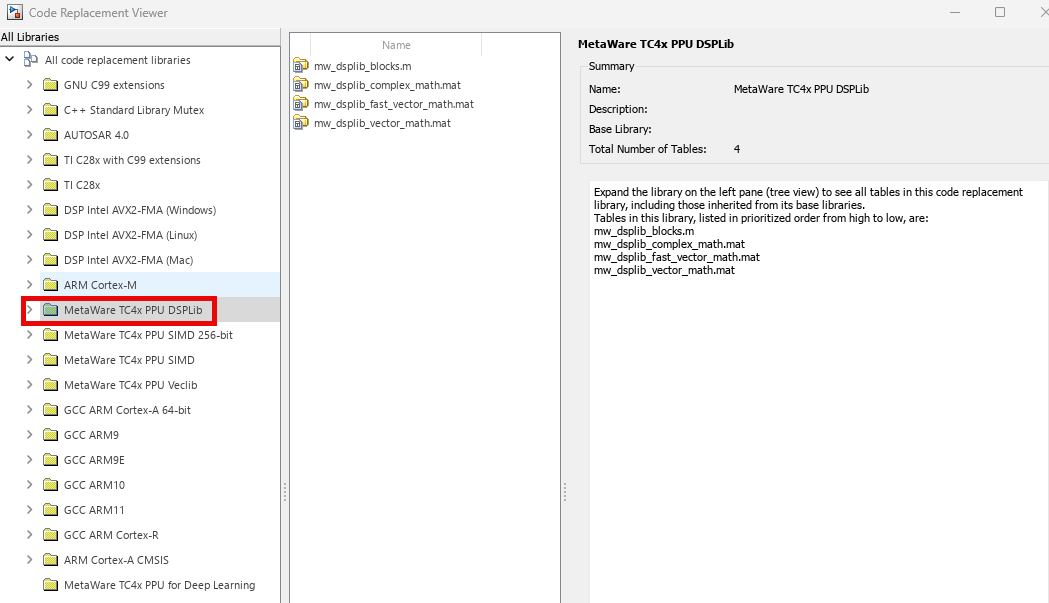

To view the available CRLs, open the Code Replacement Viewer (Simulink Coder) from the

MATLAB command window using the crviewer command. In the left

pane, select the name of a library. The viewer displays information about the library in the

right pane.

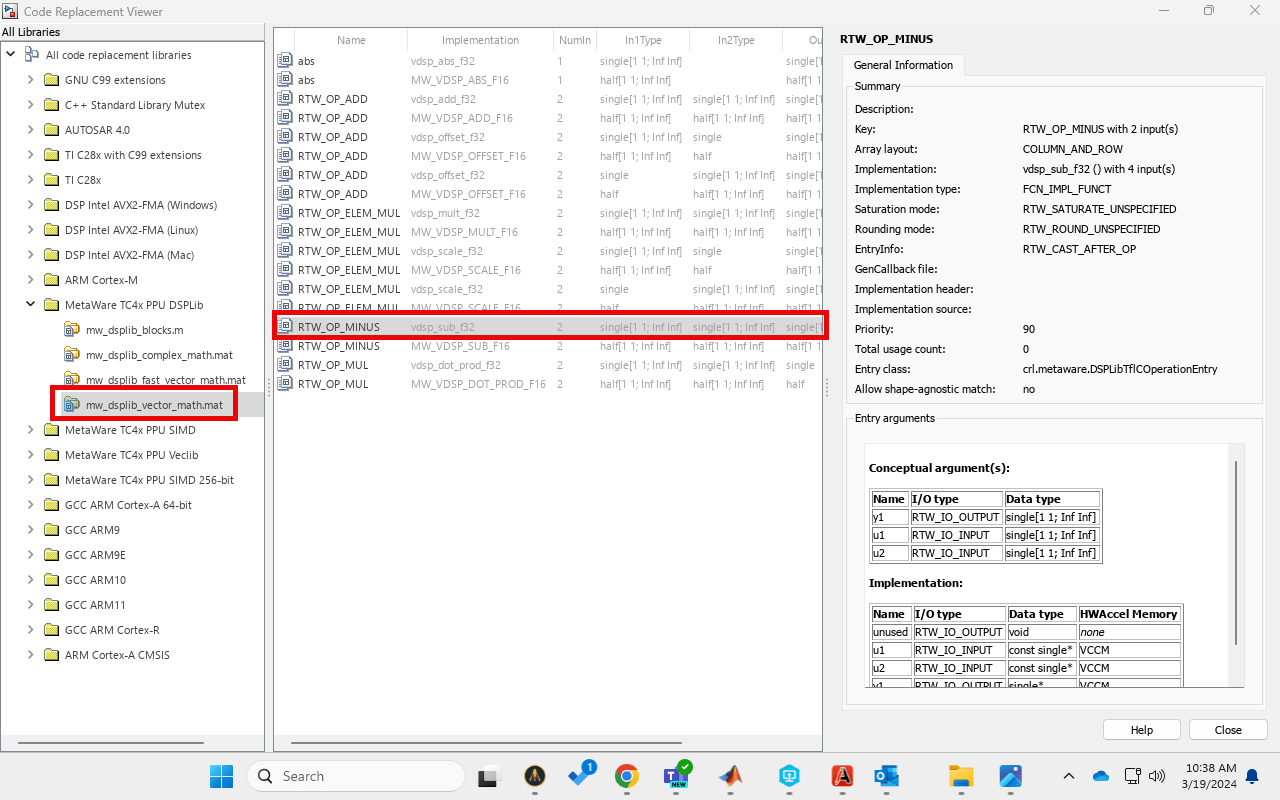

In the left pane, expand the library, explore the list of tables in the library, and select a table from the list. The middle pane displays the function and operator entries in the selected table, along with abbreviated information for each entry. In the middle pane, when you select a function or operator, the viewer displays information about that entry in the right pane.

Observe the supported data type for the available CRL entries in the middle and right panes of the code replacement viewer. Before using any CRL, ensure the data type of the application model's variables or data elements matches the required CRL entry's data type.

Select CRL and Generate Hardware-Specific Code

Follow these steps to use CRL for any PPU referenced application model:

Open the Simulink model that uses a PPU core.

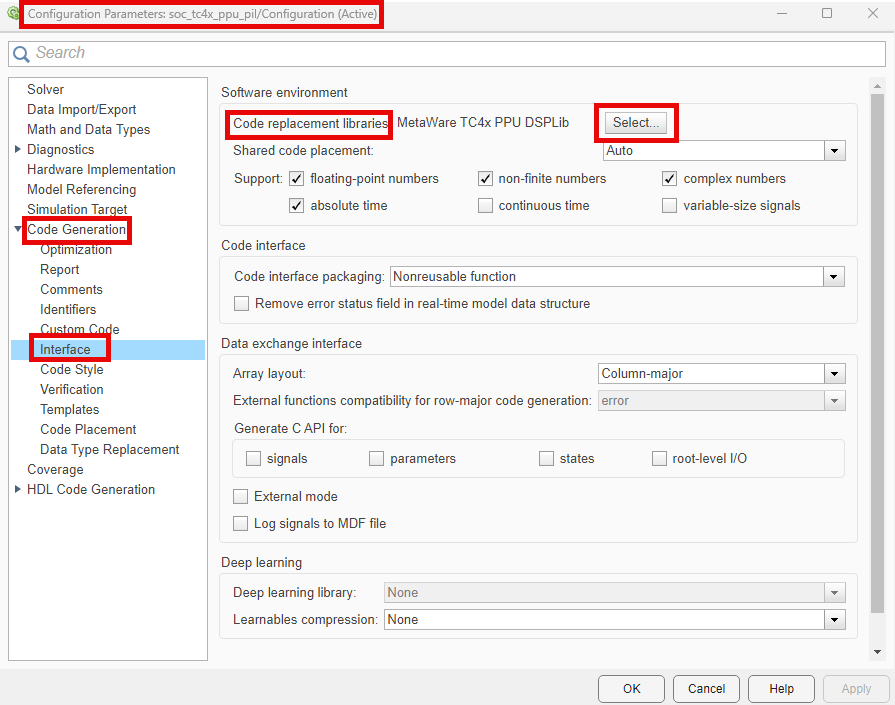

Click Ctrl+E or click Modeling > Model Settings to open the Configuration Parameters window.

Select Hardware Implementation and set the Processing Unit parameter to

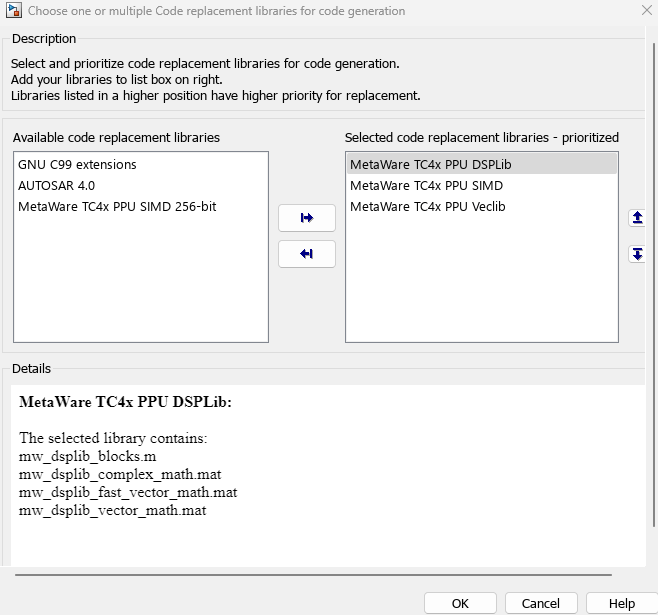

PPU.Navigate to Code Generation > Interface > Code replacement libraries and click Select to select a CRL from the libraries available for the PPU core of Infineon TC4x microcontrollers. This figure displays the CRLs available for the model in the Code Verification and Validation with PIL Using PPU example.

Use the

and

and  buttons to add and remove a CRL.

buttons to add and remove a CRL.

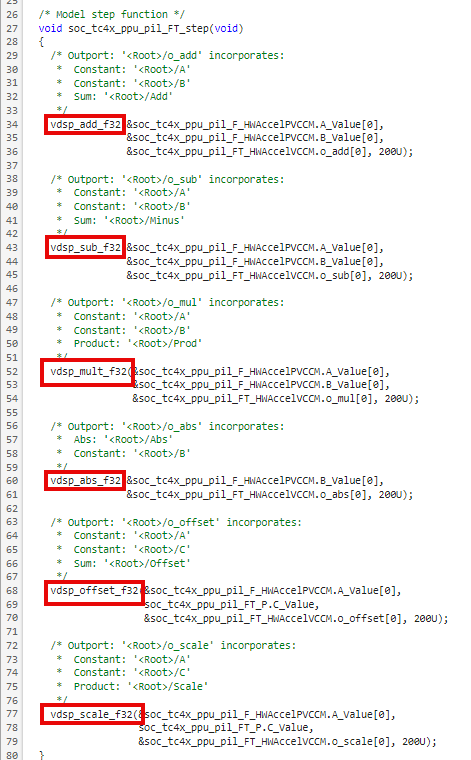

After completion of the PIL simulation steps from the Code Verification and Validation with PIL Using PPU example, this image shows the code generation report of the model with code replacements.

For PPU and TriCore based multicore models like Getting Started with PPU Acceleration for Infineon AURIX TC4x Microcontrollers, the SoC Builder tool guides you through the validate, build and run procedure. Click Configure, Build, Deploy & Start on the Hardware tab of the top model to launch the SoC Builder tool. Once you complete the build procedure, observe the code generation report with hardware-specific code replacements.

For application models running on the PPU core, the CRL assigns VCCM to the participating data. However, there can be a conflict with other memory section or storage class assigned to the same data elements by using the Embedded Coder Dictionary (Embedded Coder) and Code Mappings Editor – C (Embedded Coder). In these cases, Simulink resolves the conflict as below:

If you assign a memory section to a specific data element and the same data element is also a designated candidate for the VCCM through the CRL, then there is a conflict and the VCCM gets highest priority. The generated code contains the hardware-specific code replacements for the functions involving that data element.

If you assign storage class to a data element and the same data element is also a designated candidate for the VCCM through CRL functionality, then there is a conflict and the storage class gets highest priority. The generated code does not contain the hardware-specific code replacements for the functions involving that data element.

Known Limitations

The PPU core does not support External Mode of simulation.

The PPU core does not support C++ code generation.

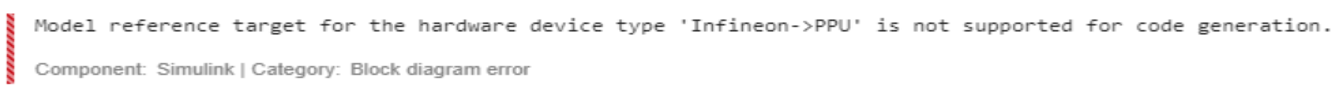

You must set the Hardware board parameter to

Infineon AURIX TC4x - TriBoardsin the Configuration Parameters window of the Simulink® model. If you set Device vendor toInfineon, Device type toPPU, and select the CRL manually while keeping the Hardware board parameter set toNone, code generation fails.The PPU core does not support model references, and Simulink displays an error message if you set the Processing Unit parameter to

PPUin the top-level model and the referenced model.

See Also

Multicore Modeling | Define Service Interfaces, Storage Classes, Memory Sections, and Function Templates for Software Architecture (Embedded Coder)