Host Interface Script Data Capture from Polyphase Channelizer Algorithm on RFSoC device

This example shows how to use the HDL-optimized Channelizer block to process incoming analog-to-digital converter (ADC) samples and produce a spectrum that has 512 MHz of bandwidth. MATLAB® displays the resulting spectrum plot by using FPGA API functions over a TCP/IP connection. The channelizer data sent back is in limited bursts, which are triggered by an AXI4 register in a capture loop. The model also contains an interface to the digital-to-analog converter (DAC) by using a numerically-controlled oscillator (NCO) to drive a tone commanded at some frequency over AXI4.

Requirements

Vivado® Design Suite. Use the supported version listed in Supported EDA Tools and Hardware.

AMD® Zynq® UltraScale+™ ZCU111, ZCU208, ZCU216, or DFE ZCU670 evaluation kit. Set up the loopback cable connections for your hardware boards. For more information, see Board-Specific Setup Information.

Open Example

Open the example project and copy the example files to a temporary folder.

1. Navigate to the example source folder by entering these commands at the MATLAB command prompt.

example_root = (hdlcoder_rfsoc_examples_root) cd (example_root)

2. Copy all of the example files in the PolyphaseChannelizer folder to a temporary folder.

Simulate Channelizer Model

To understand the channelizer model in more detail, run the simulation of rfsocChannelizer.slx and view the power spectrum view and spectrogram.

You can see the channelizer processing inside this block: rfsocChannelizer/PolyphaseChannelizer/Channelizer Receive Processing. The FFT_Capture logic captures data based off of a trigger condition called TriggerCapture, which is driven by an AXI4 register. The state machine does not wait for a trigger and processes the next available frame from the channelizer to the direct memory access (DMA). The channelizer block Start-Of-Frame and Valid control lines are used to help determine when to latch onto the frame.

Generate HDL and Synthesize Bitstream

Set up the Xilinx Vivado tool path by using hdlsetuptoolpath. Use your own Xilinx Vivado installation path when executing the command.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath', ... vivadopath);

Right-click the channelizer subsystem device under test (DUT). Select HDL Code, then click HDL Workflow Advisor. In step 1.1 of the HDL Workflow Advisor, select Target platform as Xilinx Zynq Ultrascale+ RFSoC ZCU111 Evaluation Kit, Xilinx Zynq Ultrascale+ RFSoC ZCU208 Evaluation Kit, Xilinx Zynq UltraScale+ RFSoC ZCU216 Evaluation Kit, or Xilinx Zynq UltraScale+ RFSoC DFE ZCU670 Evaluation Kit.

In step 1.2, set Reference design to Real ADC/DAC Interface. Under Reference design parameters, set these reference design parameters to the indicated values.

AXI4-Stream Master data width to

64AXI4-Stream Slave data width to

64Add external memory access (AXI4 Master) to

falseADC sampling rate (MHz) to

2048ADC decimation mode (xN) to

4ADC samples per clock cycle to

4ADC mixer type to

BypassedDAC sampling rate (MHz) to

2048DAC interpolation mode (xN) to

4DAC samples per clock cycle to

4DAC mixer type to

BypassedADC/DAC NCO mixer LO (GHz) to

DisabledEnable multi-tile sync to

false

If you are using a ZCU208, ZCU216, or ZCU670 board, additionally set the DAC DUC mode parameter to Full DUC Nyquist (0-Fs/2).

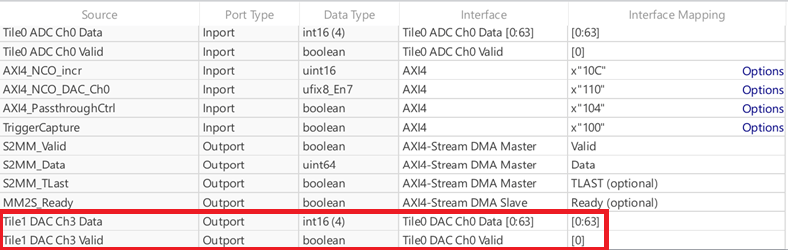

Step 1.3 shows the Target platform interface table. Set the interface mapping as shown in figure below.

If you are using a ZCU208 board, for the Tile1 DAC Ch3 Data port, set the target interface to Tile0 DAC Ch0 Data. For the Tile1 DAC Ch3 Valid port, set the target interface to Tile0 DAC Ch0 Valid.

In step 4.2, to generate a script that provides MATLAB connectivity to the board for interactive testing and live I/O interfacing, select Generate host interface script and clear the Generate Simulink software interface model checkbox.

Right-click the task 4.3 Build FPGA Bitstream, and select Run to Selected Task. This step generates the Vivado project, and builds the FPGA bitstream.

After you generates bitstream, run task 4.3 Program Target Device to program the FPGA board.

Channelizer Spectrum Data Capture

The FPGA returns the output of the channelizer, which is frequency domain data of the spectrum. The capture logic fetches a frame upon receiving the signal condition over AXI4. With the board programmed, run the script hostIO_rfsocChannelizer_interface.m.

% Data capture loop for ii=1:150 writePort(hFPGA,"TriggerCapture",false); writePort(hFPGA,"TriggerCapture",true); writePort(hFPGA,"TriggerCapture",false);

rd_data = readPort(hFPGA,"S2MM_Data");

idx = mod(ii,length(FrequencyArr)) + 1;

nco_tone = FrequencyArr(idx);

fprintf('Changing NCO Tx tone to %d MHz \n',nco_tone);

writePort(hFPGA,"AXI4_NCO_incr",uint16(incrScale*nco_tone*1e6));fft_frame = reinterp_stream_data(rd_data); spectrum = 20*log10(abs(fft_frame(1:256)));

scopeSpectrum(spectrum); scopeSpectrogram(spectrum); end

disp('Done frequency sweep');

Spectrogram and spectrum plots are displayed for 150 captures. The NCO is commanded with different tones from an array that is declared before the capture.