Specify Test Bench Clock Enable Toggle Rate

When to Specify Test Bench Clock Enable Toggle Rate

When you want the test bench to drive your input data at a slower rate than the maximum input clock enable rate, specify the test bench clock enable toggle rate.

This specification can help you to achieve better test coverage, and to simulate the real world input data rate.

Note

The maximum input clock enable rate is once every N clock cycles. N = the upsampled clock rate / original clock rate. Refer to the clock enable behavior for Input data rate, in Specify the Clock Enable Rate.

How to Specify Test Bench Clock Enable Toggle Rate

To set your test bench clock enable toggle rate:

In the HDL Workflow Advisor, select MATLAB to HDL Workflow > Code Generation.

In the Clocks & Ports tab, for the Clock enable rate option, select Input data rate.

In the Test Bench tab, for Input data interval, enter 0 or an integer greater than the maximum input clock enable interval.

Input data interval, I Test Bench Clock Enable Behavior I = 0 (default) Asserts at the maximum input clock enable rate, or once every N cycles. N = the upsampled clock rate / original clock rate. I < N Not valid; generates an error. I = N Same as I = 0. I > N Asserts every I clock cycles.

For example, this timing diagram shows clock enable behavior with Input data interval = 0. Here, the maximum input clock enable rate is once every 2 cycles.

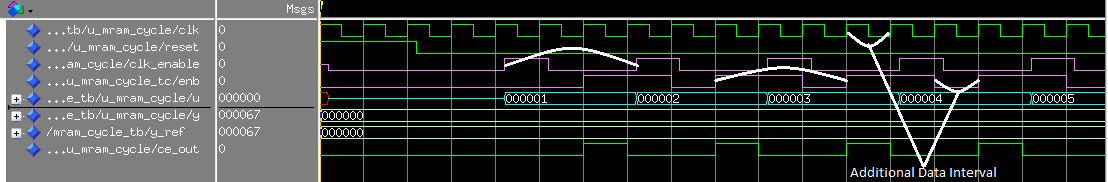

The following timing diagram shows the same test bench and DUT with Input data interval = 3.