Verify Sobel Edge Detection Algorithm in MATLAB-to-HDL Workflow

This example shows the HDL generation and verification of a MATLAB® design for the Sobel edge detection algorithm using the MATLAB HDL Coder™ Workflow Advisor. The MATLAB test bench is reused to verify the HDL using an automatically generated HDL cosimulation System object from HDL Verifier™. Any supported HDL simulator can be used, including Mentor Graphics ModelSim®/Questa®, Cadence Incisive®/Xcelium™, or Xilinx® Vivado® Simulator.

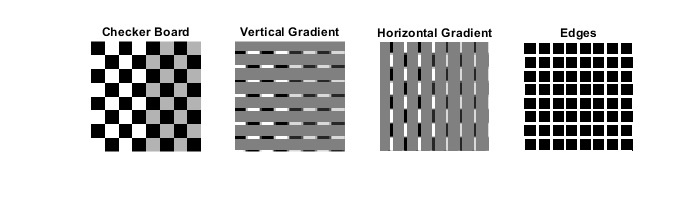

Simulate the Design

It is a good practice to simulate the design with the testbench prior to code generation to make sure there are no runtime errors.

mlhdlc_sobel_tb;

Create a New HDL Coder Project

Run the following command to create the HDL code generation project.

coder -hdlcoder -new cosim_fil_sobel

This action opens a window titled HDL Coder.

Specify the Design and the Test Bench

Drag the file

mlhdlc_sobel.mfrom the Current Folder Browser into the Entry Points tab of the HDL Coder window, under the MATLAB Function section.Under the

mlhdlc_sobel.mfile, specify the data type of input argumentdata_inasdouble (1 x 1)Drag the file

mlhdlc_sobel_tb.minto the HDL Coder window, under MATLAB Test Bench section.

Generate HDL Code

Click Workflow Advisor.

Right click on the Code Generation step in Workflow Advisor.

Choose option Run to selected task to run all steps from the beginning of the workflow through to HDL code generation.

Verify Generated HDL Code with Cosimulation

To run this step, you must have one of the HDL simulators supported by HDL Verifier. See Cosimulation Requirements (HDL Verifier). You may skip this step if you do not have access to a supported simulator.

In the Verify with Cosimulation step, perform the following steps:

Select the Generate cosimulation test bench option.

Select the Log outputs for comparison plots option. This option generates the plotting of the HDL simulator output, the reference MATLAB algorithm output, and the differences between them.

For Cosimulation tool select your HDL simulator. The HDL simulator executable must be on your system path.

To view the waveform in the HDL simulator, select GUI mode in the HDL simulator run mode in cosimulation list. For Vivado simulator there is no interactive GUI environment. To debug the HDL design, after cosimulation, open the generated file

hdlverifier_cosim_waves.wdbin Vivado.Select Simulate generated cosimulation test bench.

Click Run.

When the simulation is complete, check the comparison plots in MATLAB. There should be no mismatch between the HDL simulator output and the reference MATLAB algorithm output.

Verify Generated HDL Code with FPGA-in-the-Loop

To run this step, you must have one of the supported FPGA boards. See FPGA Verification Requirements (HDL Verifier) and Set Up FPGA Design Software Tools (HDL Verifier).

In the Verify with FPGA-in-the-Loop step, perform the following steps:

Select the Generate FPGA-in-the-Loop test bench option.

Select the Log outputs for comparison plots option. This option generates the plotting of the FPGA output, the reference MATLAB algorithm output, and the differences between them.

Select your FPGA board from the Board Name list. If your board is not on the list, click

Launch Board Managerto create a new board entry. The board manager enables adding new boards in many ways including downloading add-on support packages, cloning from existing boards, or creating one from scratch. See FPGA Board Manager (HDL Verifier).For boards using Ethernet connections enter your connection information in the Board IP Address and Board MAC Address fields.

Leave the Additional Files field empty.

Select Simulate generated FPGA-in-the-Loop test bench.

Click Run.

When the simulation is complete, check the comparison plots. There should be no mismatch between the FPGA output and the reference MATLAB algorithm output.