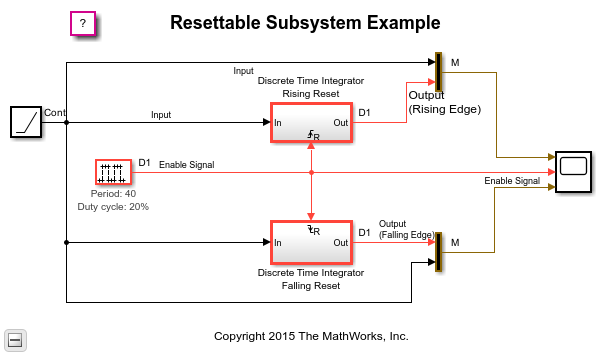

Resettable Subsystems

This example shows how to use two resettable subsystems to implement a ramp signal. Consider using resettable subsystems when you want to conditionally reset the states of all blocks within a subsystem to their initial condition. A resettable subsystem executes at every time step but conditionally resets the states of blocks within it when a trigger signal occurs at the reset port. For more information, see Using Resettable Subsystems.

After running the simulation, the scope shows three plots. The top and bottom plots show the original ramp as a reference, along with its integration. The subsystems corresponding to the top and bottom plots reset on every rising and falling edge of the pulse, respectively. When each subsystem resets, the state of the Integrator block is set to its initial condition value, which is 0. Refer to the middle plot to determine when each subsystem resets.

The reset happens for blocks within the subsystem, without the need for each block to have its own reset port. This provides a more convenient way of handling resets at a subsystem level.