AXI4-Register IIO Read (HOST)

Read memory-mapped registers into simulation model

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Common /

Host I/O

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

The AXI4-Register IIO Read (HOST) block reads value from memory-mapped registers in the programmable logic of the connected Xilinx® SoC device to a running Simulink® model on the host computer. This block enables low-latency high-throughput data transmission between your simulation model and the FPGA registers on the SoC device.

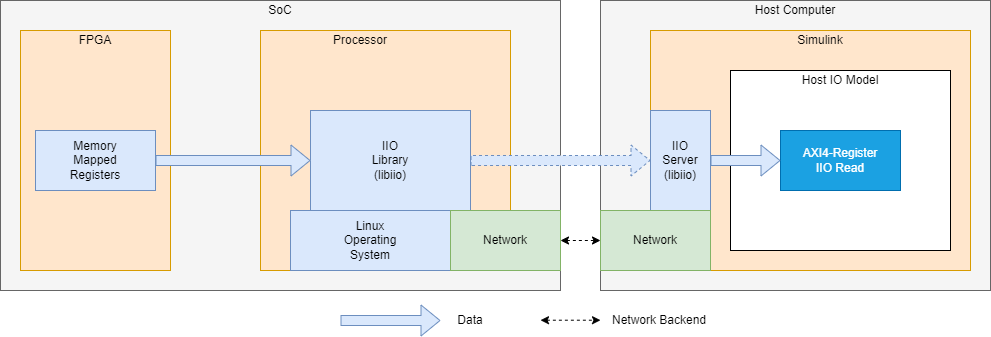

The AXI4-Register IIO Read (HOST) block receives a copy of the memory-mapped registers from the programmable logic in the SoC device on the host computer. This block uses the Industrial I/O (IIO) library driver to create a network server daemon on the SoC device and client host computer to pass the register data copies to the host computer running the simulated portion of the model. This diagram shows the connection between the memory-mapped registers, central interconnect, and communication bridge to the running Simulink model.

Ports

Output

Parameters

Version History

Introduced in R2020b