FPGA Data Capture

Capture data to MATLAB or Simulink from RFSoC devices

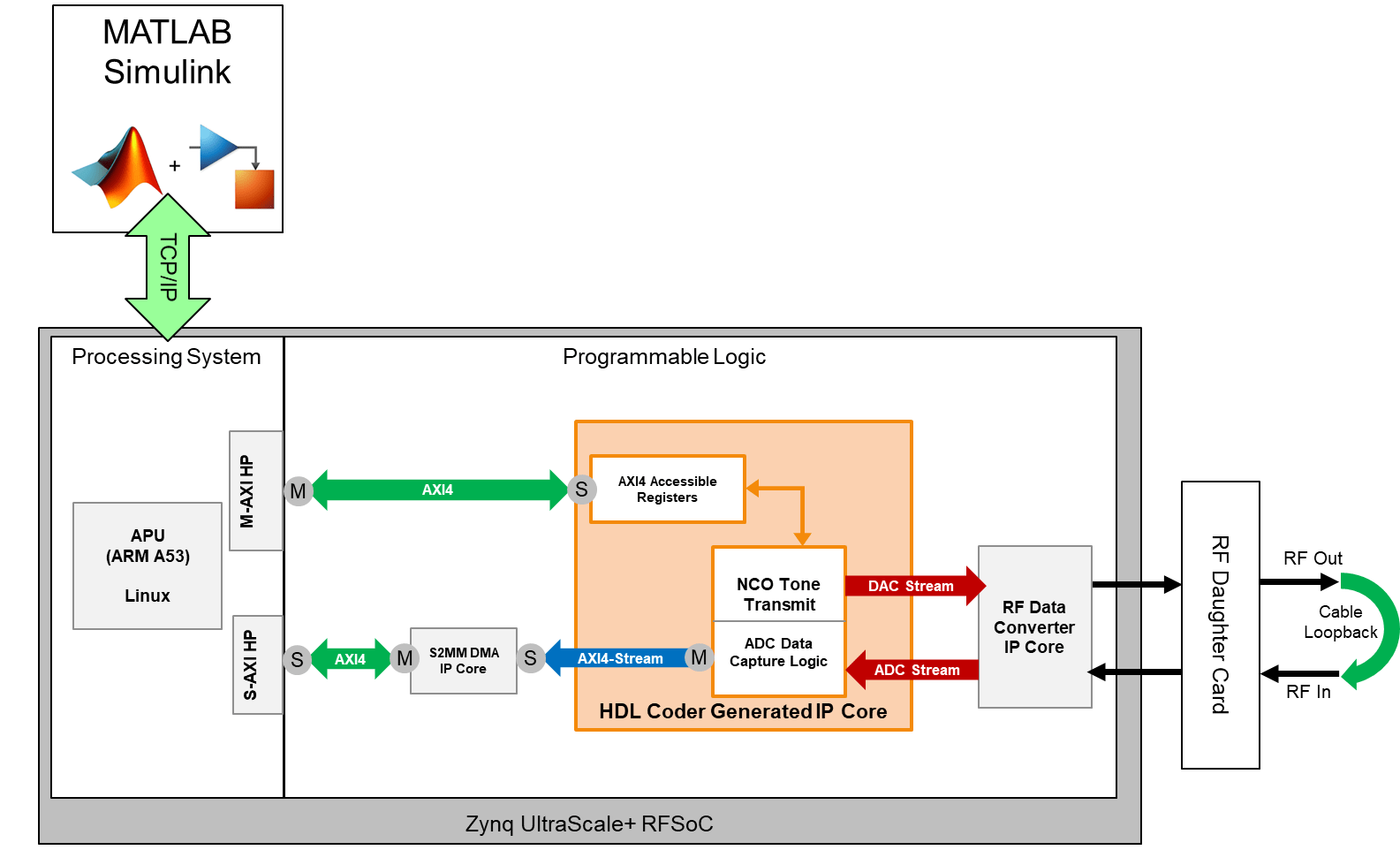

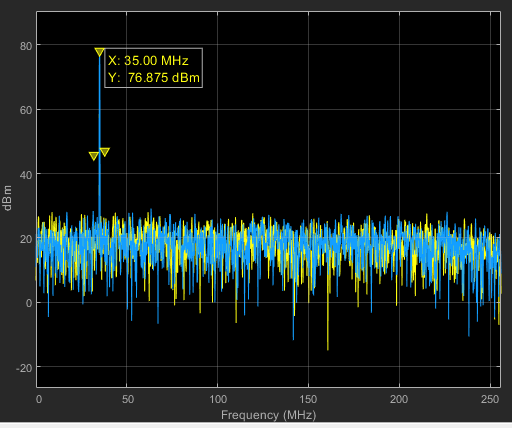

Capture raw data using FPGA input and output (IO) application programming interface (API) from an RFSoC device. Configure an SoC model for the HDL code generation by using the HDL Workflow Advisor. Generate the HDL code for your algorithm, build and deploy the HDL design on an RFSoC device, and run a MATLAB® script to interactively capture data from the deployed HDL design.

Topics

- ARM Targeting

Design and deploy algorithms to the ARM® processor.

- Reference Designs for RFSoC Devices

Learn about how to use RFSoC reference designs and their requirements.