Synthesis Results for Simscape Hardware-in-the-Loop Workflow

This example shows how to access synthesis results for Simscape™ hardware-in-the-loop (HIL) simulations using Xilinx® Vivado® tool.

Access Synthesis Results from a MAT File

You can generate HDL code for your plant models and then generate and analyze the synthesis results before deploying the generated code to the target hardware. See Simscape Hardware-in-the-Loop Workflow for guidance on each step of generating HDL code from Simscape models and deploying the generated code onto a target hardware.

Note: This page shows the synthesis results for Simscape models that use Simscape switches. It does not include the resources consumed by any additional interfaces or peripherals that are part of a complete HIL setup. You can also model these examples using dynamic switches. For more information, see sschdl.generateOptimizedModel.

This example provides synthesis results for a set of Simscape HIL workflow example models, with various data type precisions stored in the MAT file SimscapeHILExamplesResults.mat.

To access these synthesis results from this file, use:

load('SimscapeHILExamplesResults.mat');

SimscapeHILSynthesisResults

SimscapeHILSynthesisResults =

struct with fields:

HardwareDetails: [1×1 struct]

SinglePrecision: [16×5 table]

DoublePrecision: [16×5 table]

FixedPoint48Precision: [16×5 table]

FixedPoint36Precision: [16×5 table]

FixedPoint32Precision: [16×5 table]

BarGraphInfo: [1×1 struct]

SimscapeHILSynthesisResults is a structure that provides comprehensive details on the synthesis results for Simscape FPGA-based HIL simulations.

Hardware Details

To understand the synthesis tool and target hardware specifics, examine the HardwareDetails field in the SimscapeHILSynthesisResults structure.

HardwareDetails = SimscapeHILSynthesisResults.HardwareDetails

HardwareDetails =

struct with fields:

SynthesisTool: 'Xilinx Vivado'

SynthesisToolChipFamily: 'Kintex7'

SynthesisToolDeviceName: 'xc7k325t'

SynthesisToolPackageName: 'fbg676'

SynthesisToolSpeedValue: '-1'

TargetFrequency: 100

This example uses Xilinx® Vivado® synthesis tool with Kintex-7® device family as the default hardware. The Target Frequency is set to 100 MHz.

Synthesis Results for Different Data Type Precision

The synthesis results also show various precision levels — Single, Double, Fixed-Point 48, Fixed-Point 36 and Fixed-Point 32 — alongside model-specific metrics such as model sample time and the utilization percentages of lookup tables (LUTs), registers, and digital signal processors (DSPs).

Single-Precision Results

To retrieve single precision synthesis results in the SimscapeHILSynthesisResults structure, use:

SinglePrecisionTable = SimscapeHILSynthesisResults.SinglePrecision

SinglePrecisionTable =

16×5 table

Model Sample Time (us) LUTs utilization (%) Registers utilization (%) DSPs utilization (%) RAMs utilization (%)

______________________ ____________________ _________________________ ____________________ ____________________

sschdlexBoostConverterModel 0.534 7.28 3.2 5 0

sschdlexBridgeRectifierModel 0.416 9.56 4.16 7.02 0

sschdlexBuckBoostConverterModel 0.475 6.75 2.97 4.76 0

sschdlexBuckConverterModel 0.283 6.08 2.66 4.76 0

sschdlexCukConverterModel 0.532 18.24 7.87 13.69 0

sschdlexDCMotorPartitionSolverModel 0.897 5.86 2.24 2.86 0

sschdlexFlybackConverterModel 0.71 13.96 6.01 10.12 0

sschdlexHalfWaveRectifierModel 0.121 0.88 0.48 0.95 0

sschdlexNonlinearTransformerModel 0.438 7.14 3.21 5.12 0

sschdlexNPCBridgeModel 0.918 16.97 7.44 12.74 0

sschdlexPMSMPartitionSolverModel 1.189 43.61 17.17 21.67 0

sschdlexPushPullConverterModel 0.78 21.6 9.89 15.83 0

sschdlexResonantLLCConverterModel 0.532 18.44 7.73 13.33 0

sschdlexSEPICConverterModel 0.59 16.11 6.98 12.02 0

sschdlexSolarInverterPartitionedNetworkModel 1.984 23.93 10.68 13.21 0

sschdlexThreePhaseRectifierModel 0.814 11.68 5.07 7.74 0

Double-Precision Results

To retrieve double precision synthesis results in the SimscapeHILSynthesisResults structure, use:

DoublePrecisionTable = SimscapeHILSynthesisResults.DoublePrecision

DoublePrecisionTable =

16×5 table

Model Sample Time (us) LUTs utilization (%) Registers utilization (%) DSPs utilization (%) RAMs utilization (%)

______________________ ____________________ _________________________ ____________________ ____________________

sschdlexBoostConverterModel 0.785 16.38 7.03 24.64 0

sschdlexBridgeRectifierModel 0.614 21.64 9.18 32.14 0

sschdlexBuckBoostConverterModel 0.699 15.17 6.43 23.57 0

sschdlexBuckConverterModel 0.443 13.74 5.82 21.43 0

sschdlexCukConverterModel 0.728 27.35 12 41.79 0

sschdlexDCMotorPartitionSolverModel 0.944 10.39 4.05 14.4 0

sschdlexFlybackConverterModel 1.049 31.52 13.17 46.07 0

sschdlexHalfWaveRectifierModel 0.186 2.08 1.06 4.29 0

sschdlexNonlinearTransformerModel 0.742 16.33 6.88 25.71 0

sschdlexNPCBridgeModel 1.22 27.41 12.25 41.79 0

sschdlexPMSMPartitionSolverModel 1.884 67.37 26.22 75.36 0

sschdlexPushPullConverterModel 0.985 38.17 16.43 54.64 0

sschdlexResonantLLCConverterModel 0.856 27.42 11.25 33.21 0

sschdlexSEPICConverterModel 0.814 27.14 12.13 42.86 0

sschdlexSolarInverterPartitionedNetworkModel 2.141 43.25 18.53 41.79 0

sschdlexThreePhaseRectifierModel 1.049 25.9 11 35.36 0

48-Bit Fixed-Point Precision Results

To access the synthesis results for models using fixed-point with a 48-bit word length, you can retrieve the data from the FixedPoint48Precision field in the SimscapeHILSynthesisResults structure:

Fixed48PrecisionTable = SimscapeHILSynthesisResults.FixedPoint48Precision

Fixed48PrecisionTable =

16×5 table

Model Sample Time (us) LUTs utilization (%) Registers utilization (%) DSPs utilization (%) RAMs utilization (%)

______________________ ____________________ _________________________ ____________________ ____________________

sschdlexBoostConverterModel 0.045 2 0.15 16.43 0

sschdlexBridgeRectifierModel 0.041 2.47 0.19 22.86 0

sschdlexBuckBoostConverterModel 0.042 1.76 0.13 13.93 0

sschdlexBuckConverterModel 0.032 1.51 0.14 18.21 0

sschdlexCukConverterModel 0.048 4.69 0.24 38.57 0

sschdlexDCMotorPartitionSolverModel 2.051 3.26 0.71 11.19 0

sschdlexFlybackConverterModel 0.066 3.46 0.21 37.5 0

sschdlexHalfWaveRectifierModel 0.024 0.23 0.07 2.14 0

sschdlexNonlinearTransformerModel 1.666 3.3 0.8 16.43 0

sschdlexNPCBridgeModel 0.07 4.17 0.26 47.14 0

sschdlexPMSMPartitionSolverModel 6.678 34.99 9.47 68.33 0

sschdlexPushPullConverterModel 0.067 16.23 0.34 57.38 0

sschdlexResonantLLCConverterModel 0.057 4.13 0.22 57.86 0

sschdlexSEPICConverterModel 0.047 3.66 0.19 48.93 0

sschdlexSolarInverterPartitionedNetworkModel 0.238 6.92 1.15 54.29 0

sschdlexThreePhaseRectifierModel 0.072 2.25 0.26 18.93 0

36-Bit Fixed-Point Precision Results

To access the synthesis results for models using fixed-point with a 36-bit word length, you can retrieve the data from the FixedPoint36Precision field in the SimscapeHILSynthesisResults structure:

Fixed36PrecisionTable = SimscapeHILSynthesisResults.FixedPoint36Precision

Fixed36PrecisionTable =

16×5 table

Model Sample Time (us) LUTs utilization (%) Registers utilization (%) DSPs utilization (%) RAMs utilization (%)

______________________ ____________________ _________________________ ____________________ ____________________

sschdlexBoostConverterModel 0.041 1.58 0.11 6.19 0

sschdlexBridgeRectifierModel 0.037 2.03 0.15 8.81 0

sschdlexBuckBoostConverterModel 0.039 1.48 0.1 5.71 0

sschdlexBuckConverterModel 0.028 0.97 0.1 7.62 0

sschdlexCukConverterModel 0.042 3.21 0.17 17.14 0

sschdlexDCMotorPartitionSolverModel 1.621 3.01 0.67 5.48 0

sschdlexFlybackConverterModel 0.058 2.1 0.16 15.48 0

sschdlexHalfWaveRectifierModel 0.021 0.15 0.05 0.71 0

sschdlexNonlinearTransformerModel 1.351 2.8 0.76 7.26 0

sschdlexNPCBridgeModel 0.064 2.38 0.18 16.9 0

sschdlexPMSMPartitionSolverModel 5.402 28.87 8.91 37.38 0

sschdlexPushPullConverterModel 0.06 3.85 0.26 41.43 0

sschdlexResonantLLCConverterModel 0.051 2.87 0.16 25.71 0

sschdlexSEPICConverterModel 0.044 2.36 0.13 15.95 0

sschdlexSolarInverterPartitionedNetworkModel 0.219 5.37 0.81 23.93 0.56

sschdlexThreePhaseRectifierModel 0.066 1.72 0.2 6.9 0

32-Bit Fixed-Point Precision Results

To access the synthesis results for models using fixed-point with a 32-bit word length, you can retrieve the data from the FixedPoint32Precision field in the SimscapeHILSynthesisResults structure:

Fixed32PrecisionTable = SimscapeHILSynthesisResults.FixedPoint32Precision

Fixed32PrecisionTable =

16×5 table

Model Sample Time (us) LUTs utilization (%) Registers utilization (%) DSPs utilization (%) RAMs utilization (%)

______________________ ____________________ _________________________ ____________________ ____________________

sschdlexBoostConverterModel 0.039 1.01 0.09 3.81 0

sschdlexBridgeRectifierModel 0.037 1.62 0.13 8.81 0

sschdlexBuckBoostConverterModel 0.039 1.14 0.09 5 0

sschdlexBuckConverterModel 0.028 0.77 0.09 7.62 0

sschdlexCukConverterModel 0.042 2.47 0.15 17.14 0

sschdlexDCMotorPartitionSolverModel 1.568 2.85 0.65 5 0

sschdlexFlybackConverterModel 0.057 1.57 0.13 15.48 0

sschdlexHalfWaveRectifierModel 0.021 0.12 0.05 0.71 0

sschdlexNonlinearTransformerModel 1.288 2.55 0.74 5.95 0

sschdlexNPCBridgeModel 0.063 1.85 0.16 16.9 0

sschdlexPMSMPartitionSolverModel 5.223 28.3 8.77 37.38 0

sschdlexPushPullConverterModel 0.061 3.02 0.23 40.71 0

sschdlexResonantLLCConverterModel 0.051 1.99 0.15 20.48 0

sschdlexSEPICConverterModel 0.043 1.84 0.1 15.24 0

sschdlexSolarInverterPartitionedNetworkModel 0.219 4.16 0.71 22.62 0.56

sschdlexThreePhaseRectifierModel 0.068 1.34 0.17 6.43 0

Bar Graph Info

The SimscapeHILSynthesisResults structure contains a field, BarGraphInfo, that aids in visualizing and comparing the synthesis results of the same example model across different data type precisions. To access the BarGraphInfo, use:

BarGraphInfo = SimscapeHILSynthesisResults.BarGraphInfo

BarGraphInfo =

struct with fields:

sschdlexBoostConverterModel: [1×1 struct]

sschdlexBridgeRectifierModel: [1×1 struct]

sschdlexBuckBoostConverterModel: [1×1 struct]

sschdlexBuckConverterModel: [1×1 struct]

sschdlexCukConverterModel: [1×1 struct]

sschdlexDCMotorPartitionSolverModel: [1×1 struct]

sschdlexFlybackConverterModel: [1×1 struct]

sschdlexHalfWaveRectifierModel: [1×1 struct]

sschdlexNonlinearTransformerModel: [1×1 struct]

sschdlexNPCBridgeModel: [1×1 struct]

sschdlexPMSMPartitionSolverModel: [1×1 struct]

sschdlexPushPullConverterModel: [1×1 struct]

sschdlexResonantLLCConverterModel: [1×1 struct]

sschdlexSEPICConverterModel: [1×1 struct]

sschdlexSolarInverterPartitionedNetworkModel: [1×1 struct]

sschdlexThreePhaseRectifierModel: [1×1 struct]

The BarGraphInfo is a structure that contains several fields, with each field dedicated to storing the synthesis results for a specific example model and is named accordingly. For example, the fields sschdlexBoostConverterModel and sschdlexBridgeRectifierModel store the synthesis results for the models boost converter model and bridge rectifier model, respectively.

To retrieve and analyze the synthesis results for the boost converter model from the BarGraphInfo field in the SimscapeHILSynthesisResults structure, enter:

BoostConverterResults = SimscapeHILSynthesisResults.BarGraphInfo.sschdlexBoostConverterModel

BoostConverterResults =

struct with fields:

LUTs: [16.3800 7.2800 2 1.5800 1.0100]

Registers: [7.0300 3.2000 0.1500 0.1100 0.0900]

DSPs: [24.6400 5 16.4300 6.1900 3.8100]

RAMs: [0 0 0 0 0]

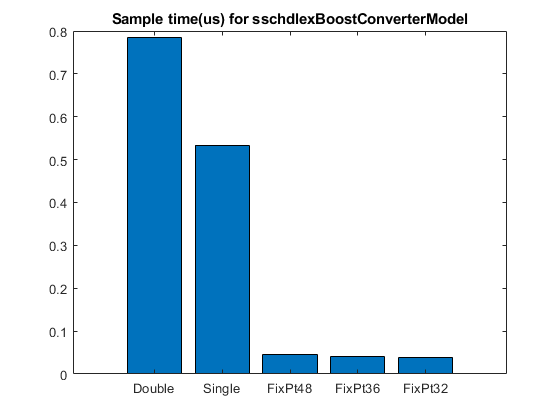

SampleTime: [0.7850 0.5340 0.0450 0.0410 0.0390]

The structure corresponding to a specific model, such as BoostConverterResults, contains detailed information about resource usage including LUTs, Registers, DSPs, and RAMs, along with the sample time across several data types such as double, single and fixed-point with 48, 36 and 32-bit word lengths respectively.

Visualizing Results with Various Data Type Precisions

To compare the performance of the Boost Converter Model across different data type precisions, visualizing the sample time data is key. By plotting this data as a bar graph to observe how the sample time of the model varies with precision changes, use:

bar(BoostConverterResults.SampleTime); set(gca,'XTickLabel',["Double", "Single", "FixPt48", "FixPt36", "FixPt32"]); title('Sample time(us) for sschdlexBoostConverterModel'); % for better readability

See Also

sschdl.generateOptimizedModel | sschdladvisor | hdladvisor | sschdl.updateRuntimeParameters