Data Converters

Simulate and analyze performance metrics of analog-to-digital (ADC) and digital-to-analog (DAC) data converters. Start from complete system-level models of typical ADC or DAC architectures. Modify ADC or DAC parameters to achieve your desired system specifications.

After designing the data converter, you can validate your design using Measurements and Testbenches. You can also analyze your models using MATLAB® functions. For more information, see Analysis and Optimization.

Functions

Blocks

Topics

- Compare SAR ADC to Ideal ADC

This example compares the SAR ADC block from Mixed-Signal Blockset™ to the ideal ADC model with impairments presented in Analyzing Simple ADC with Impairments.

- Design and Evaluate Interleaved ADC Using System Object

This example shows how to use System objects to model and evaluate the performance of an interleaved ADC.

- Effect of Metastability Impairment in Flash ADC

This example shows how to customize a flash Analog to Digital Converter (ADC) by adding the metastability probability as an impairment.

- Compare Binary-Weighted DAC to Ideal DAC

This example compares the Binary Weighted DAC block from the Mixed-Signal Blockset™ to an ideal DAC model.

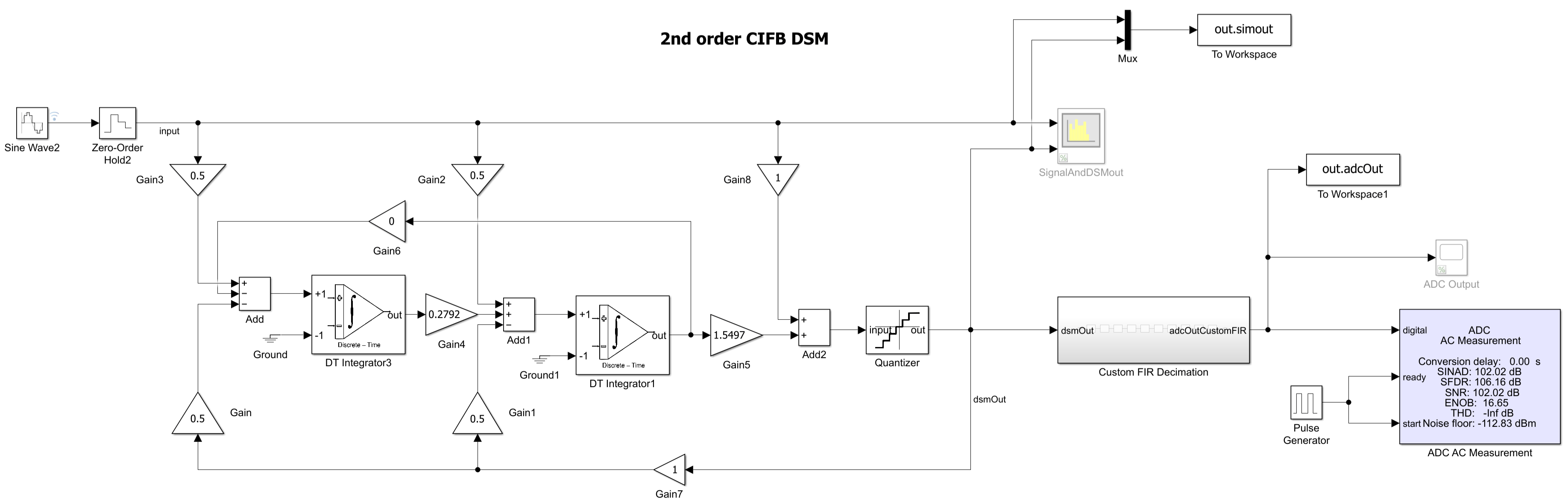

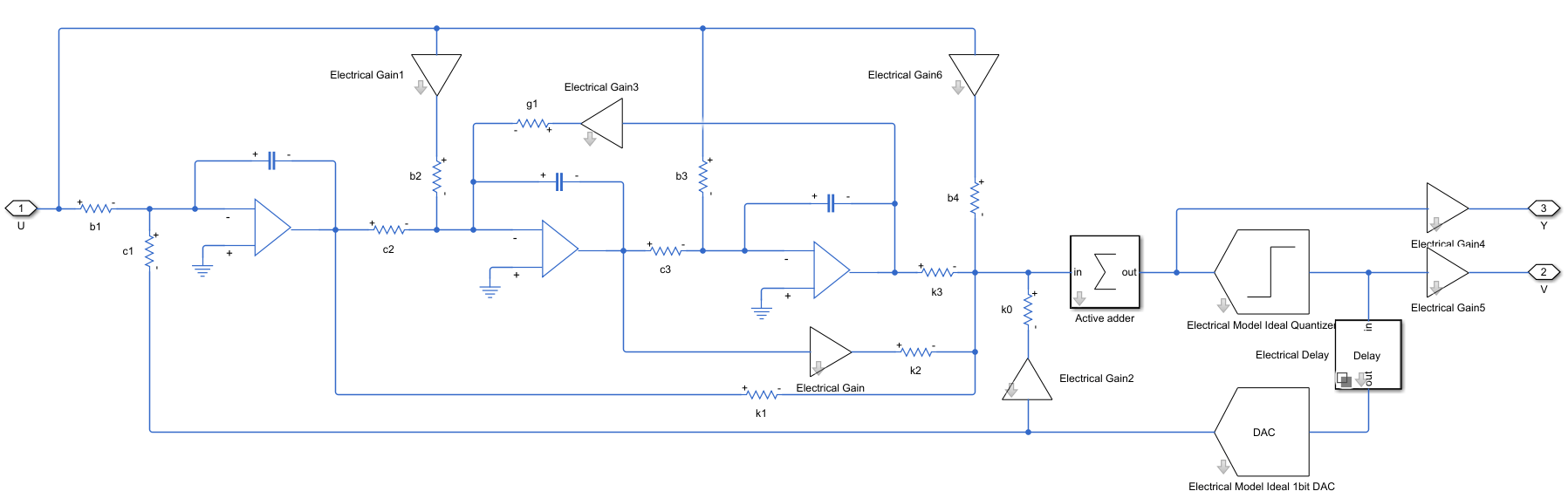

- ADC Tutorial

This tutorial example shows you how to design a second-order delta-sigma analog-to-digital converter in Simulink®.

- STEP 1: System-Level Model of DSM ADC

- STEP 2: SystemVerilog Module Generation

- STEP 3: Final System-Level Model